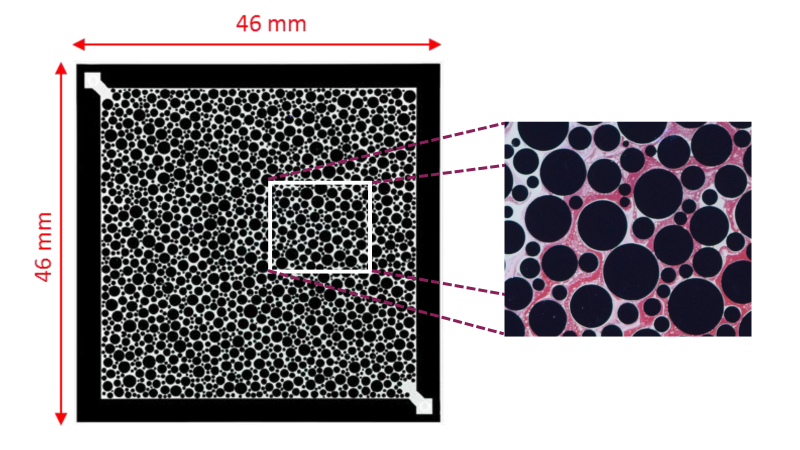

Silicon-glass hybrid chips typically compose of a silicon layer which contains dry etched structures, bonded with a plain or structured glass layer. Anodic bonding creates hermetically sealed chips without the use of adhesives or intermediate layers. The glass layer is fully transparent, while the silicon layer is not transparent for visible light (only for infrared).

Usually hybrid chips consist of a crystalline silicon layer combined with:

-

BF33 glass

-

MEMPax glass

Benefits of hybrid chips

-

Bonding is done without additives (anodic): no autofluorescence or compatibility issues

-

Optical transparency on one side (glass-si)

-

Optical transparency on both the top and bottom when using a triple stack (glass-si-glass)

In hybrid chips, the action usually takes place on the silicon layer, where the relevant structures are applied. This can be a system of microfluidic channels or, for example, a pillar structure. The most commonly used etching methods to create these structures are Reactive Ion Etching (RIE) and Deep Reactive Ion Etching (DRIE).

Silicon etching

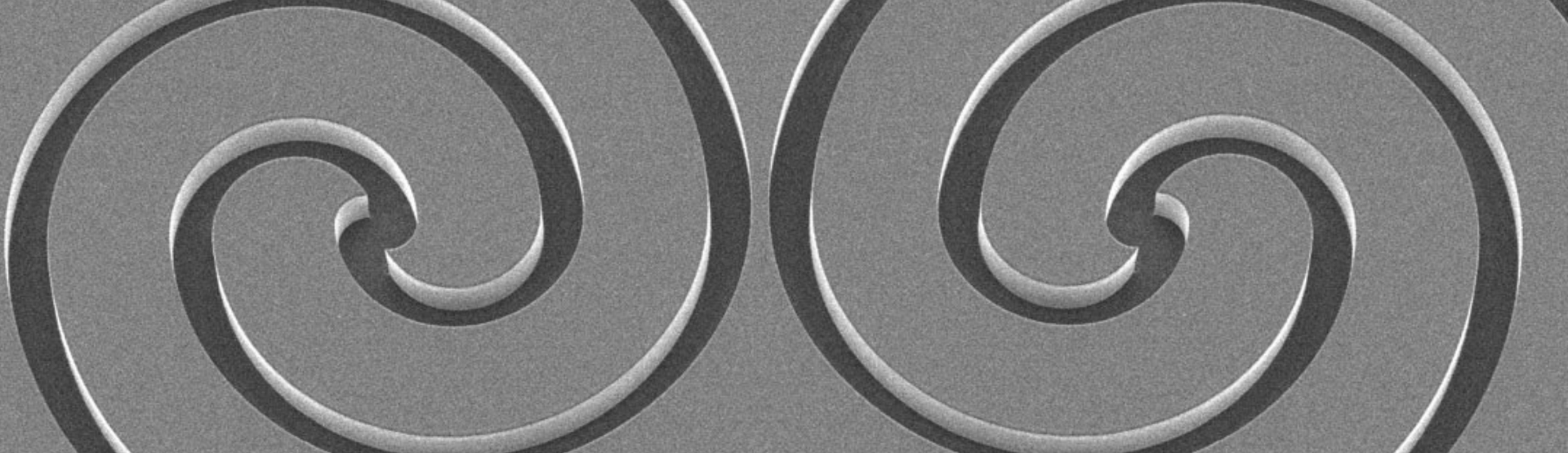

Reactive ion etching (RIE) is a specific etching technique, typically used when high aspect ratio structuring is required. RIE can generate deep structures and steep side walls: ultimate examples of anisotropic etching. But it can also be used to produce through silicon vias (TSV’s).

RIE is a dry etching process, performed with gases. Along the process, the gas molecules are broken up into ions, which bombard the surface of the wafer or substrate to create the desired structure.

At Micronit, we specialize in Deep Reactive Ion Etching (DRIE), using the Bosch process. This process consists of alternating etching and passivation steps. This cycle of steps is repeated just as long as it takes to reach the desired etch depth or through hole.

Benefits of RIE/DRIE

-

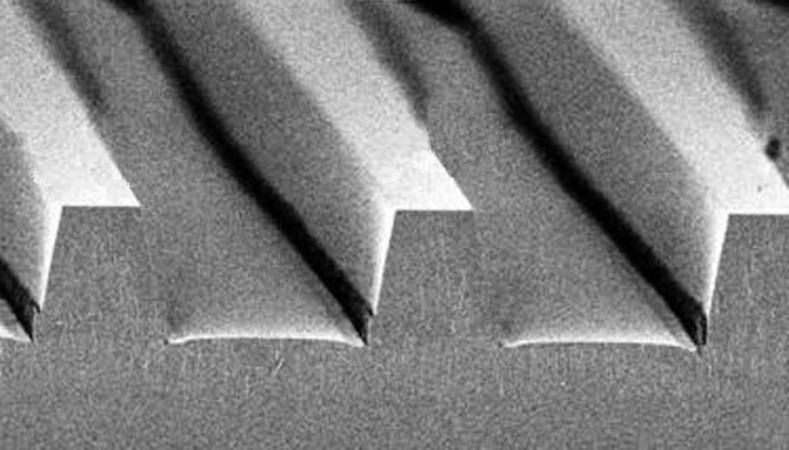

Large design freedom:

-

aspect ratios up to 1:50 (width versus height) are within reach

-

walls are not curved but straight

-

angles closely approach 90°, usually with a slight taper of 1-3 degrees

-

-

Very smooth channel walls

-

Highly accurate structures

-

Good chemical compatibility